Texas Instruments TMS320VC5510A Fixed-Point DSPs

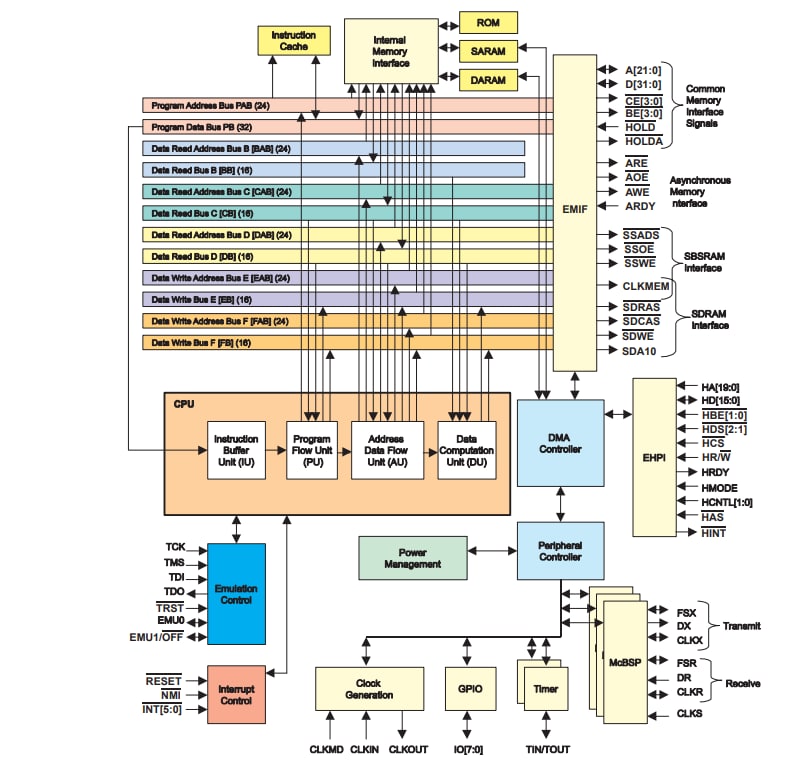

Texas Instruments TMS320VC5510A Fixed-Point Digital Signal Processors are based on the TMS320C55x DSP generation CPU processor core. These devices feature a C55x™DSP architecture that achieves high performance and low power through increased parallelism and a total focus on reducing power dissipation. The CPU supports an internal bus structure that includes one program bus, three data read buses, two data write buses, and additional buses dedicated to peripheral and DMA activity. These buses can perform up to three data reads, and two data writes in a single cycle. In parallel, the DMA controller can perform up to two data transfers per cycle independent of the CPU activity.The TI TMS320VC5510A C55x CPU provides two multiply-accumulated (MAC) units capable of 17-bit x 17-bit multiplication in a single cycle. An additional 16-bit ALU supports a central 40-bit arithmetic/logic unit (ALU). The use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the address unit (AU) and the data unit (DU) of the C55x CPU.

The TMS320C55x DSP core was created with an open architecture that allows application-specific hardware to boost performance on specific algorithms. The extensions enable the TMS320VC5510A to deliver exceptional video codec performance with more than half its bandwidth for performing additional functions such as color space conversion, user-interface operations, security, TCP/IP, voice recognition, and text-to-speech conversion.

Features

- High-performance, low-power, fixed-point TMS320C55x™; Digital Signal Processor (DSP)

- 6.25/5ns instruction cycle time

- 160/200MHz clock rate

- One/two instructions are executed per cycle

- Dual multipliers (up to 400 million multiply-accumulates per second (MMACS))

- Two arithmetic/logic units

- One internal program bus

- Three internal data/operand read buses

- Two internal data/operand write buses

- Instruction cache (24K bytes)

- 160K x 16-bit on-chip RAM composed of

- Eight blocks of 4K × 16-bit dual-access RAM (DARAM) (64K bytes)

- 32 blocks of 4K × 16-bit single-access RAM (SARAM)(256K bytes)

- 32-bit external memory interface (EMIF) with a glueless interface to

- Asynchronous static RAM (SRAM)

- Asynchronous EPROM

- Synchronous DRAM (SDRAM)

- Synchronous burst SRAM (SBSRAM)

- 16K × 16-bit on-chip ROM (32K bytes)

- 8M × 16-bit maximum addressable external memory space

- Programmable low-power control of six device functional domains

- On-chip peripherals

- Two 20-bit timers

- Six-channel direct memory access (DMA) controller

- Three multichannel buffered serial ports (McBSPs)

- 16-bit parallel enhanced host-port interface (EHPI)

- Programmable digital phase-locked loop (DPLL) clock generator

- Eight general-purpose I/O (GPIO) pins and dedicated general-purpose output (XF)

- On-chip scan-based emulation logic

- IEEE Std 1149.1 (JTAG) boundary-scan logic

- 240-terminal MicroStar BGA™; (ball grid array) (GGW suffix)

- 240-terminal MicroStar BGA™; (ball grid array) (ZGW suffix) [lead-free]

- 3.3V I/O supply voltage

- 1.6V core supply voltage

Applications

- Compression

- Video processing

- Machine vision

- Medical imaging

Additional Resources

Block Diagram