Infineon Technologies AURIX™ 32-bit TC4Dx Microcontrollers

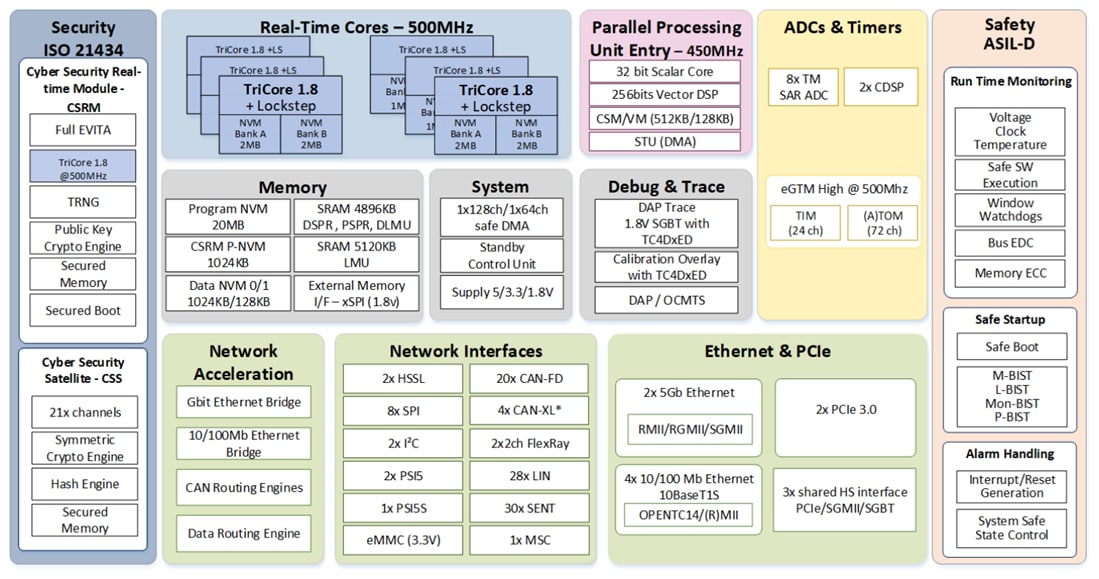

Infineon Technologies AURIX™ 32-bit TC4Dx Microcontrollers are based on 28nm technology and are part of the AURIX TC4x family. Implemented the 28nm technology, the TC4Dx delivers excellent D7 high-speed connectivity for zone controllers, integration platforms, and safety applications. The Infineon AURIX 32-bit TC4Dx MCUs supply 6/6 lockstep cores at 500MHz, up to 20MB non-volatile memory in eFlash technology, 10MB SRAM, and robust connectivity features including two 5Gbps and four 10/100Mbps Ethernet interfaces. To address the demand for high-speed communication and interfaces, TC4Dx features a rich connectivity setup to 2x 5Gbit Ethernet, including a bridge, 4x 10/100Mbit Ethernet, 20 CAN nodes, 4x CAN-XL, and up to 2x8 Gbit PCle 3.0.Features

- High-performance microcontroller with six CPU cores and one parallel processing unit (vector DSP)

- CPUs are 32-bit super-scalar TriCore™ CPUs (TC1.8 LS) with virtual machine hardware support and double precision floating point arithmetic; six fully lock-stepped cores

- Low-latency SRAMs close to the CPUs and global SRAM

- 20MB of embedded program memory with multiple parallel banks and an A/B swap option

- Up to 1152KB of embedded data NVM

- High-performance cybersecurity architecture with 1MB of program memory and 128KB of data memory

- Two DMA controllers, each with 128/64 channels, and two move engines

- ADC sub-system with eight SAR ADC cores, each two ADC cores sharing 16 inputs equipped with a sample and hold stage (TMADC), two embedded DSP cores for flexible post-processing of ADC results (CDSP)

- An eGTM timer unit with input and output channels

- High-speed communication interfaces (LETH, GETH, PCle, CANXL, xSPI, HSSL, SDMMC)

- Low-speed communication interfaces (CAN, FlexRay, QSPI, ASCLIN, I2C)

- Sensor interfaces (MSC, SENT, PSI5, PSI5-S)

- Sophisticated interrupt system with an interrupt router and ECC

- Safety and Security Alarm Management Unit (SMU) handles safety and cybersecurity alarms

- Advanced trace and debug with support of run control debugging for multi-core and time-aligned multi-core programs, and data trace for all CPUs in parallel, and a 5Gbps high-speed serial trace interface

- Support of two DAP (Device Access Port) interfaces and one JTAG interface

- Digital programmable IO ports

- Volatile Memory Test (VMT) unit with ECC, memory initialization, and MBIST functions

- Power Management System and on-chip regulators

- Clock generation unit with system PLL and peripheral PLL

- Embedded voltage regulators

- AEC-Q100, grade 1 qualified for automotive applications

Applications

- Zone controller

- Domain controller

- Gateway

- ADAS/AD and sensor fusion

- Safety companion for central computing

Specifications

- 6/6 lockstep cores

- 500MHz core frequency

- Up to 20MB eFlash

- Up to 10MB SRAM

- Up to 15x increase in performance

- Up to eight virtual machines per core

- 20+4 CAN FD and CAN XL interfaces

- 4x 10/100Mb ethernet modules

- 2x 5Gbps Ethernet module

- Up to 60 analog input pins

Block Diagram

Publicado: 2025-07-16

| Actualizado: 2025-08-28